Hardware Reference

In-Depth Information

Data I/O Bus

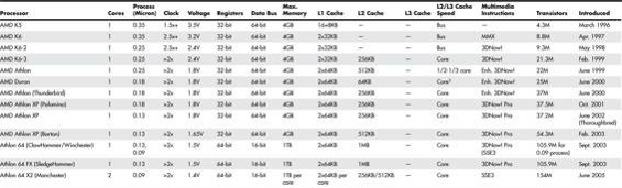

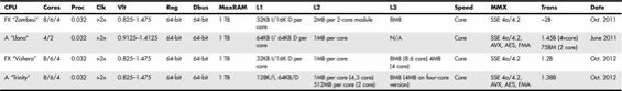

Two of the more important features of a processor are the speed and width of its external data bus.

These define the rate at which data can be moved into or out of the processor.

Data in a computer is sent as digital information in which certain voltages or voltage transitions

occurring within specific time intervals represent data as 1s and 0s. You can increase the amount of

data being sent (called

bandwidth

) by increasing either the cycling time or the number of bits being

sent at a time, or both. Over the years, processor data buses have gone from 8 bits wide to 64 bits

wide. The more wires you have, the more individual bits you can send in the same interval. All

modern processors from the original Pentium and Athlon through the latest Core i7, AMD FX 83xx

series, and even the Itanium series have a 64-bit (8-byte)-wide data bus. Therefore, they can transfer

64 bits of data at a time to and from the motherboard chipset or system memory.

A good way to understand this flow of information is to consider a highway and the traffic it carries.

If a highway has only one lane for each direction of travel, only one car at a time can move in a

certain direction. If you want to increase the traffic flow (move more cars in a given time), you can

either increase the speed of the cars (shortening the interval between them), add more lanes, or both.

As processors evolved, more lanes were added, up to a point. You can think of an 8-bit chip as being

a single-lane highway because 1 byte flows through at a time. (1 byte equals 8 individual bits.) The

16-bit chip, with 2 bytes flowing at a time, resembles a two-lane highway. You might have four lanes

in each direction to move a large number of automobiles; this structure corresponds to a 32-bit data

bus, which has the capability to move 4 bytes of information at a time. Taking this further, a 64-bit

data bus is like having an eight-lane highway moving data in and out of the chip.

After 64-bit-wide buses were reached, chip designers found that they couldn't increase speed further,

because it was too hard to synchronize all 64 bits. It was discovered that by going back to fewer

lanes, it was possible to increase the speed of the bits (that is, shorten the cycle time) such that even

greater bandwidths were possible. Because of this, many newer processors have only 4-bit or 16-bit-

wide data buses, yet they have higher bandwidths than the 64-bit buses they replaced.