Hardware Reference

In-Depth Information

provides present a severe limitation. Installing several devices that need the services of system IRQs

in a PC/XT-type system can be a study in frustration because the only way to resolve the interrupt-

shortage problem is to remove the adapter board that you need the least.

16-Bit ISA, EISA, and MCA Bus Interrupts

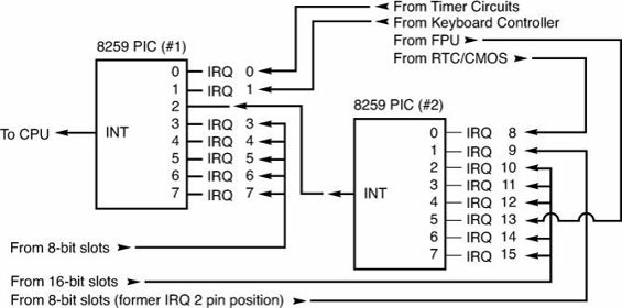

The introduction of the AT, based on the 286 processor, was accompanied by an increase in the

number of external hardware interrupts the bus would support. The number of interrupts was doubled

to 16 by using two Intel 8259 interrupt controllers, piping the interrupts generated by the second one

through the unused IRQ2 in the first controller. This arrangement effectively makes only 15 IRQ

assignments available, and IRQ2 effectively became inaccessible.

By routing all the interrupts from the second IRQ controller through IRQ2 on the first, all these new

interrupts are assigned a nested priority level between IRQ1 and IRQ3. Thus, IRQ15 ends up having

a higher priority than IRQ3.

Figure 4.47

shows how the two 8259 chips were wired to create the

cascade through IRQ2 on the first chip.

Figure 4.47. Interrupt controller cascade wiring.

To prevent problems with boards set to use IRQ2, the AT system designers routed one of the new

interrupts (IRQ9) to fill the slot position left open after removing IRQ2. This means that any card you

install in a more recent system that claims to use IRQ2 is really using IRQ9 instead.

Table 4.60

shows the typical uses for interrupts in the 16-bit ISA and 32-bit PCI/AGP buses and lists

them in priority order from highest to lowest. The obsolete EISA and MCA buses used a similar IRQ

map.

Table 4.60. 16/32-Bit ISA/PCI/AGP Default Interrupt Assignments